全国2010年4月高等教育计算机系统结构自考试题

《自考视频课程》名师讲解,轻松易懂,助您轻松上岸!低至199元/科!

在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均不得分。

1.在计算机系统结构设计中,提高软件功能实现的比例可( )

A.提高解题速度

B.减少需要的存储器容量

C.提高系统的灵活性

D.提高系统的性能价格比

2.浮点数表示的尾数的基rm=16,尾数长度p=8,可表示的规格化最大正尾数的值是( )

A.1/256

B.1/2

C.15/16

D.255/256

3.下列数据存储空间为隐含寻址方式的是( )

A.CPU中的通用寄存器

B.主存储器

C.I/O接口中的寄存器

D.堆栈

4.当计算机系统执行通道程序完成输入输出工作时,执行通道程序的是( )

A.CPU

B.通道

C.CPU和通道

D.指定的外设

5.下列有关中断的叙述正确的是( )

A.中断响应的次序是由硬件决定的

B.中断处理的次序是由硬件决定的

C.中断处理的次序是不可改的

D.中断响应的次序是可灵活改变的

6.与虚拟存储器的等效访问速度无关的是( )

A.访存页地址流

B.页面替换算法

C.主存的容量

D.辅存的容量

7.非线性流水线的特征是( )

A.一次运算中使用流水线中的多个功能段

B.一次运算中多次使用流水线中的某些功能段

C.流水线中某些功能段在各次运算中的作用不同

D.流水线的各功能段在不同的运算中可以有不同的连接

8.属于集中式共享存储器结构的SIMD计算机是( )

A.ILLIAC IV

B.BSP

C.CM-2

D.MP-1

9.指令执行结果出现异常而引起的中断是( )

A.程序性中断

B.I/O中断

C.机器校验中断

D.外部中断

10.下列关于脉动阵列机的描述,错误的是( )

A.脉动阵列机是由一组内部结构相同的处理单元构成的阵列

B.脉动阵列机结构简单、规整,模块化强,可扩充性好

C.脉动阵列机不适用于要求计算量大的信号/图像的处理

D.脉动阵列机各PE间数据通信距离短、规则,使数据流和控制流的设计、同步控制等均简单、规整

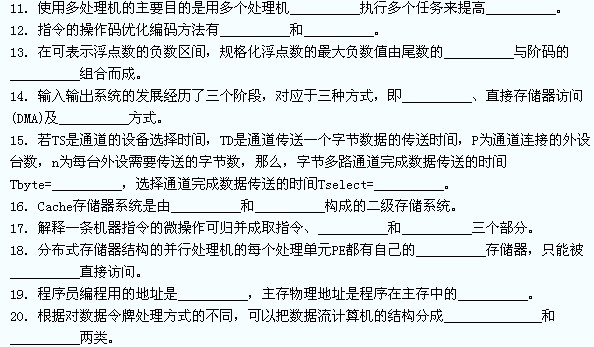

二、填空题(本大题共10小题,每小题2分,共20分)

请在每小题的空格中填上正确答案。错填、不填均不得分。

三、简答题(本大题共5小题,每小题6分,共30分)

21.简述实现软件移植的统一高级语言途径存在的问题。

22.简述设计RISC结构采用的基本技术。

23.设某系统的中断源的中断请求优先级分为4级,从高到低为l、2、3、4。设中断级屏蔽位为“1”,对应屏蔽;中断级屏蔽位为“0”,对应开放。要求中断处理次序与中断响应次序相同,请给出各级中断处理程序中断级屏蔽位的设置。(要求:先进行文字说明,再画出中断级屏蔽位表)

24.设指令由取指、分析、执行和存结果四个子部件组成,每个子部件经过时间为 t,连续执行12条指令。画出在度m为3的超流水线处理机上工作的时空图。

25.画出ILLIAC IV处理单元的互连结构,用PUi表示第i个处理单元(i=0,l,…,63)。

四、简单应用题(本大题共2小题,每小题10分,共20分)

26.设有一条3段流水线,各段执行时间依次为△t、3△t和△t。

(1)分别计算连续输入3条指令和连续输入30条指令时的实际吞吐率和效率。

(2)将瓶颈段细分为3个独立段,各子段执行时间均为At,分别计算改进后的流水线连续输入3条指令和连续输入30条指令时的实际吞吐率和效率。

(3)比较(1)和(2)的结果,给出结论。

27.在多处理机上,给定表达式为:E=a(b+c(d+e(f+gh))),利用减少树高来尽可能加快运算速度,求

(1)画出在3台处理机上并行运算的树形流程图。

(2)当处理机数P=3时,确定运算级数Tp、单处理机级数T1、加速比SP和效率EP的值。

五、综合应用题(本大题共2小题,每小题10分,共20分)

28.一个由高速缓冲存储器与主存储器组成的二级存储系统,已知主存容量为1M字,高速缓存容量为32K字。采用组相联地址映象与变换,缓存共分8组,主存与缓存的块的大小均为64字。

(1)画出主存与缓存的地址格式,说明各字段名称与位数。

(2)假设缓存的存取周期为20ns,命中率为0.95,采用缓存后的加速比要达到10,计算主存的存取周期。

29.具有N=2n个输入端的omega网络,采用单元控制。

(1)N个输出端总共有多少种不同的排序?以N=3为例说明。

(2)限定只能用omega网络一次,可以实现多少种输入端与输出端不发生冲突的不同置换连接?

(3)N=8时,计算omega网络只使用一次能实现的置换连接数占全部可能的置换连接数的百分比。

本文标签:江西自考 计算机系统结构 全国2010年4月高等教育计算机系统结构自考试题

转载请注明:文章转载自(http://www.zikao.jx.cn)

《江西自考网》免责声明:

1、由于各方面情况的调整与变化,本网提供的考试信息仅供参考,考试信息以省考试院及院校官方发布的信息为准。

2、本网信息来源为其他媒体的稿件转载,免费转载出于非商业性学习目的,版权归原作者所有,如有内容与版权问题等请与本站联系。联系邮箱:812379481@qq.com